# Design of 1.7 to 14kV Normally-Off Trenched and Implanted Vertical JFET in 4H-SiC

X. Li<sup>1,2</sup> and J. H. Zhao<sup>2</sup>

<sup>1</sup> United Silicon Carbide, Inc, 100 Jersey Ave, Building A, New Brunswick, NJ08901, USA <sup>2</sup> SiCALB, ECE Dept., Rutgers University, 94 Brett Road, Piscataway, NJ 08854, USA

Keywords: SiC, Vertical JFET, and Numerical Simulation.

**Abstract.** In this paper, a high voltage normally-off trenched-and-implanted vertical JFET (TI-VJFET) in 4H-SiC is investigated by way of two-dimensional numerical simulations. The structure is simple to fabricate and is expected to be able to achieve a high current density. Detailed designs are presented for 1.7kV to 14kV normally-off 4H-SiC VJFETs. A good agreement has been reached between computer modeling and experimental 1.7kV normally-off TI-VJFET in 4H-SiC. The fabricated 1.7kV device shows a  $V_B^2/R_{on,sp}$  value of 827MW/cm<sup>2</sup> at room temperature, which represents a substantial performance improvement to the state-of-the-art.

# Introduction

In recent years, a large effort has been devoted to the development of SiC power switches because they are expected to drastically outperform their Si counterparts for high power and high temperature applications. Among the unipolar power switching devices, SiC MOSFET and JFET have recently been investigated intensively. SiC JFET is advantageous over SiC MOSFET in that SiC MOSFET currently suffers from low channel mobility [1] and may have reliability problems when operated under both high electric fields and high temperatures [2]. This paper presents the design of a high-voltage normally-off trenched-and-implanted vertical JFET (TI-VJFET) in 4H-SiC. In comparison to previously reported VJFETs [3,4], this device is simpler to fabricate because it (i) does not need the expensive epitaxial re-growth, (ii) eliminates the lateral JFET, making it possible to achieve near theoretical performance over a wide voltage range, and (iii) only one mask requires critical alignment. It is shown that this structure can be readily used to fabricate TI-VJFETs with different blocking capabilities in a single fabrication run by simply using the appropriate thickness and doping concentration for the drift layer. The TI-VJFET structure is optimized using ISE-TCAD device simulator with the physical models of 4H-SiC as depicted in [5]. A good agreement has been reached between theoretical and experimental 1.7kV normally-off 4H-SiC TI-VJFET.

# **Device Structure of 14kV TI-VJFET**

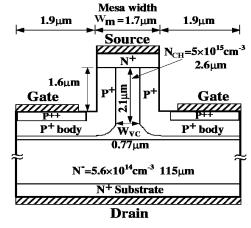

The cross sectional view of the 14kV TI-VJFET is shown in Fig.1. This structure has been optimized to block over 14kV in normally-off mode by performing a lot of trial simulations. It consists of three N-type epilayers. The top heavily doped N<sup>+</sup> epilayer is used for the source ohmic contact. The middle N-type epilayer, which has a thickness of 2.6µm and a doping concentration of  $5 \times 10^{15}$  cm<sup>-3</sup>, is used to form the vertical channel. The vertical channel is designed to be completely depleted at zero gate bias at both room temperature (RT) and 200°C so that the device can operate in normally-off mode up to 200°C. The bottom

Fig.1. 14kV TI-VJFET cell structure.

#### 1198

lightly doped N<sup>-</sup> layer, which has a thickness of  $115\mu$ m and a doping concentration of  $5.6 \times 10^{14}$  cm<sup>-3</sup>, is used to support high drain voltage. The deep gate trench is to be created by using ICP etching. Multi-step Al-implantation can be applied to form the vertical channel and P<sup>+</sup> trench bottom for gate ohmic contact.

### DC Characterization of 14kV TI-VJFETs

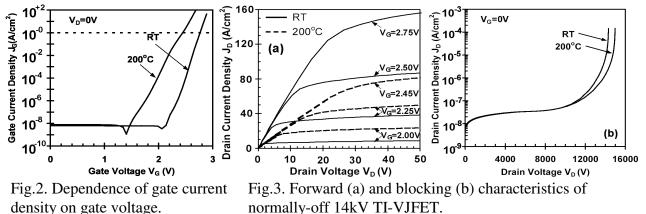

**Gate Voltage.** To turn on the device, a positive voltage must be applied on the gate to forward bias the junction between the gate  $P^+$  region and the N-type channel layer. The maximum gate voltage that can be used to turn on the device is limited by the allowed maximum gate current density, which is set to be  $1A/cm^2$  in this work. Therefore, the maximum gate voltage used to turn on the device is 2.75V and 2.45V at RT and 200°C, respectively, as depicted in Fig.2.

**Forward and Blocking Characteristics**. The forward and blocking characteristics of the optimized device are presented in Fig.3. At RT, the forward current density is 33.9A/cm<sup>2</sup> at V<sub>D</sub> equal to 5V, corresponding to a specific on-resistance of 147.5m $\Omega \cdot$ cm<sup>2</sup>, which is close to the specific on-resistance (139.5m $\Omega \cdot$ cm<sup>2</sup>) of the drift layer. Obviously, the drift layer resistance dominates the device total on-resistance. At 200°C, the forward current density is 14.24A/cm<sup>2</sup> at V<sub>D</sub> equal to 5V, corresponding to a specific on-resistance of 351m $\Omega \cdot$ cm<sup>2</sup>. It is seen from Fig.3b that the device can block 14,316V and 14,976V in normally-off mode at RT and 200°C, respectively.

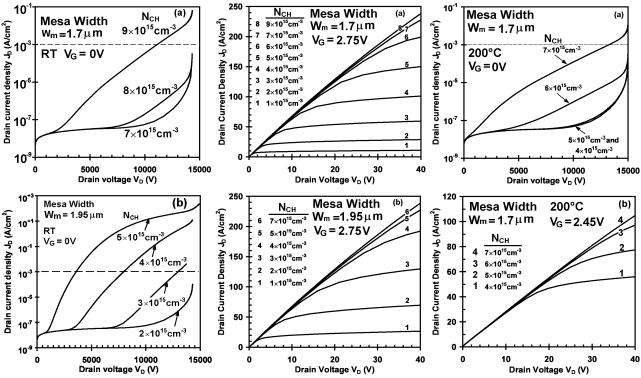

### Design of Mesa Width (W<sub>m</sub>) and Vertical Channel Doping Concentration (N<sub>CH</sub>)

For a normally-off device, the leakage current density in off-state should be as low as possible. In this design, the maximum allowed leakage current density is set to be  $1\text{mA/cm}^2$ . The effects of  $W_m$  and  $N_{CH}$  on the device blocking characteristics at RT are shown in Fig.4. The vertical channel opening  $W_{VC}$  at  $N=5\times10^{15}\text{cm}^{-3}$  is 0.77 $\mu$ m and 1.02 $\mu$ m for  $W_m$  equal to 1.7 $\mu$ m and 1.95 $\mu$ m, respectively. It is seen from Fig.4 that, to keep the leakage current density lower than  $1\text{mA/cm}^2$  at 14kV, the maximum  $N_{CH}$  must be lower than  $9\times10^{15}$  cm<sup>-3</sup> and  $3\times10^{15}$  cm<sup>-3</sup> for  $W_m$  equal to 1.7 $\mu$ m and 1.95 $\mu$ m, respectively. It also can be seen from Fig.4 that  $N_{CH}$  has almost no effect on the avalanche breakdown voltage. This makes it possible to design the channel layer and blocking layer separately for high voltage normally-off TI-VJFETs.

To optimize  $W_m$  (or  $W_{VC}$ ) and  $N_{CH}$ , their effects on the device forward characteristics are simulated and presented in Fig.5. For  $W_m = 1.7\mu m$  ( $W_{VC} = 0.77\mu m$  at  $N=5\times10^{15} cm^{-3}$ ), the drain current density does not saturate for  $V_D$  up to 40V when  $N_{CH}$  is larger than  $7\times10^{15} cm^{-3}$ . But, for  $W_m$ = 1.95 $\mu m$  ( $W_{VC} = 1.02\mu m$  at  $N=5\times10^{15} cm^{-3}$ ), the drain current density saturates at a relatively low current density of  $130A/cm^2$  even when the maximum allowed  $N_{CH}$  of  $3\times10^{15} cm^{-3}$  is used. Therefore,  $W_m$  should not be too wide. A  $W_m$  of 1.7 $\mu$ m is a good choice.  $W_m$ , however, can not be too small because it is difficult to process.

Because the device is designed to operate up to 200°C, the effects of  $W_m$  and  $N_{CH}$  on the device characteristics at 200°C for  $W_m = 1.7\mu m$  are simulated and shown in Fig.6. It is seen that the leakage current density at 14kV is slightly larger than  $1mA/cm^2$  when  $N_{CH} = 7 \times 10^{15} cm^{-3}$ . Thus, the maximum allowed  $N_{CH}$  is about  $7 \times 10^{15} cm^{-3}$  in order to keep the device normally off at both RT and 200°C. Considering the fact that the doping concentration in commercial wafer could be 50% off the expected value, a  $N_{CH}$  of  $5 \times 10^{15} cm^{-3}$  is used in the optimized 14kV TI-VJFET.

Fig.4. Effects of mesa width and Fig.5. Effects of mesa width and Fig.6. Effects of channel doping<br/>concentration on channel doping concentration on concentration on the blocking<br/>the blocking characteristics of<br/>14kV TI-VJFET at RT.Fig.6. Effects of channel doping<br/>concentration on the blocking<br/>characteristics of<br/>the forward characteristics of<br/>14kV TI-VJFET at RT.VJFET at Q0°C.

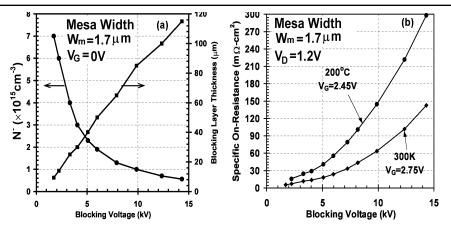

#### Drift Layer Design for 1.7 to 14kV TI-VJFETs

Different blocking capabilities can be realized for the TI-VJFET shown in Fig.1 by simply using the proper thickness  $W_D$  and doping concentration N<sup>-</sup> for the drift layer without changing the gate and source design. For punch through structure,  $W_D$  and N<sup>-</sup> can be optimized to give the lowest specific on-resistance. The optimized  $W_D$  and N<sup>-</sup> for different voltage normally-off TI-VJFETs and the corresponding specific on-resistance of the TI-VJFETs at RT and 200°C are shown in Fig.7. When the blocking voltage is lower than 3kV, it is seen from Fig.7 that N<sup>-</sup> is close to or even larger than the optimized N<sub>CH</sub> = 5×10<sup>15</sup> cm<sup>-3</sup>. Thus, the same doping concentration is used in the channel layer and the blocking layer in Fig.7 when the blocking voltage is lower than 3kV.

#### **Comparison between Modeling and Experimental Results**

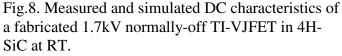

A 1.7kV normally-off 4H-SiC TI-VJFET has been demonstrated experimentally. Detailed fabrication steps can be found in [6]. The measured DC characteristics are presented in Fig.8. A near theoretical blocking voltage ( $V_{bl}$ ) of 1,726V has been achieved with a low specific on-resistance of

0.35

0.30

0.25

300K

$3.6 \text{m}\Omega\text{-cm}^2$ . giving a  $V_{bl}^{2}/R_{on,sp}$ value of 827MW/cm<sup>2</sup>, which represents a substantial performance improvement to the state-of-the-art. Simulations have been performed to evaluate the vertical channel mobility, as shown in Fig.8. A good between agreement the experimental and modeling results is obtained when the channel electron mobility is  $561 \text{cm}^2/\text{Vs}$ , W<sub>VC</sub> is 0.63µm,

Fig.7. Optimized drift layer for 1.7 to 14kV TI-VJFETs (a) and corresponding device specific on-resistance.

and N<sub>CH</sub> is  $6.5 \times 10^{15}$  cm<sup>-3</sup>, which are very close to the designed values.

#### **Summary**

1.7kV to 14kV 4H-SiC normally-off TI-VJFETs have been designed and optimized by performing a large number of numerical simulations. A good agreement between theoretical and experimental results has been achieved for a 1.7kV TI-VJFET and channel electron mobility, opening and doping concentration have been evaluated.

#### Current Density J<sub>b</sub> (A/ Drain Current I<sub>D</sub> (A) 0.10 0.10 Channel mobility μ\_**=561cm²/Vs** 150 1741V 10<sup>7</sup>×I<sub>D</sub> 2.781V (3.0V) 100 Drain 1726V 0.05 2.5V (2.5V) 50 100×I. 0V (0V) 0.00 0 500 1000 1500 2000 0 2 3 5 Drain Voltage V (V)

V<sub>c</sub>=Simulations (Measurements)

2.954V (5.0V)

2.936V (4.5V)

2.914V (4.0V

350

300

250

200

Measured

Simulated

In simulations:

W<sub>vc</sub>=0.63µm

N=6.5×10<sup>15</sup>cm<sup>-3</sup>

### Acknowledgement

This work has been supported in part by a

DARPA SBIR program (Contract No. DAAH01-01-C-R2000) managed by Dr. John Zolper.

#### References

[1] J. A. Cooper, Jr., M. R. Melloch, R. Singh, A. Agarwal, and J. W. Palmour: IEEE Trans. Electron Devices, Vol. 49 (2002), p.665.

[2] M. M. Maranowski and J. A. Cooper, Jr.: IEEE Trans. Electron Devices, Vol. 46 (1999), p.520.

[3] P. Friedrichs, H. Mitlehner, R. Schörner, K.-O. Dohnke, R. Elpelt, and D. Stephani, Materials Science Forum, 2002, vols. 389-393, p. 1185-1188.

[4] K. Asano, Y. Sugawara, S. Ryu, R. Singh, J. Palmour, T. Hayashi, and D. Takayama, ISPSD 2001, p.23-26

[5] J. H. Zhao, X. Li, K. Tone, P. Alexandrov, M. Pan and M. Weiner: Solid-State Electronics, Vol. 47 (2003), p.377-384

[6] J. H. Zhao, K. Tone, X. Li, P. Alexandrov, L. Fursin and M. Weiner : ISPSD 2003, Cambridge, UK, p.50-53.